HLS学习

前言

FPGA又称可编程逻辑门阵列,因为其魔法的并行计算和魔法的可编程逻辑单元阵列,让我产生了兴趣。目前在学数电和verilog。一个月前小伙伴达成共识,要做一个参赛项目。在那个项目里面要全用verilog写的话……恕我直言!太难了(T▽T)。所以就开始学这个HLS,在用C转verilog的边缘试探。讲点正经的,这些技术工具本身就是在用户体验感的路上走了!跑了!加速了!底层的东西因为不符合普通人类思维,所以越走越窄。换个角度来说,也可以看做掌握底层的人越来越少。至于这个稀少带来的是价值提升还是被边缘化,这个还是要用发展的眼光去看的。至少现在我认为verilog/VHDL是不能抛弃的,并不是说学了HLS就用不着这些了。HLS也好,verilog/VHDL也好都有其局限性。最关键的还是使用这些工具的人自身的能力和经验。

HLS基础介绍

高层次综合(HLS)是指自动综合最初用C、C++或SystemC语言描述的数字设计。工程师之所以对高层次综合如此感兴趣,不仅是因为它能让工程师在较高的抽象层面上工作,而且还因为它能方便地生成多种设计解决方案。利用HLS,您能探索各种可能性,分析面积和性能特点,最终确定一个方案在FPGA芯片上实现算法。举例来说,您能探索将存储器映射到Block RAM(BRAM)或分布式RAM上有什么不同的影响,或者分析回路展开以及其它回路相关优化有什么效果,而且不必手动生成不同的寄存器传输级(RTL)设计。您所要做的仅仅是在C/C++/SystemC设计中设置相关指令而已。

赛灵思在其最新发布的Vivado™工具套件中推出了HLS工具。Vivado HLS是AutoESL工具的品牌转型重塑,可提供众多技术帮助您优化C/C++/SystemC代码以实现目标性能。这样的HLS工具就能帮助您在FPGA上快速实现算法,无需借助基于Verilog和VHDL等硬件描述语言的非常耗时的RTL设计方法。

HLS入门学习资料

第一, 手边的学习资料。

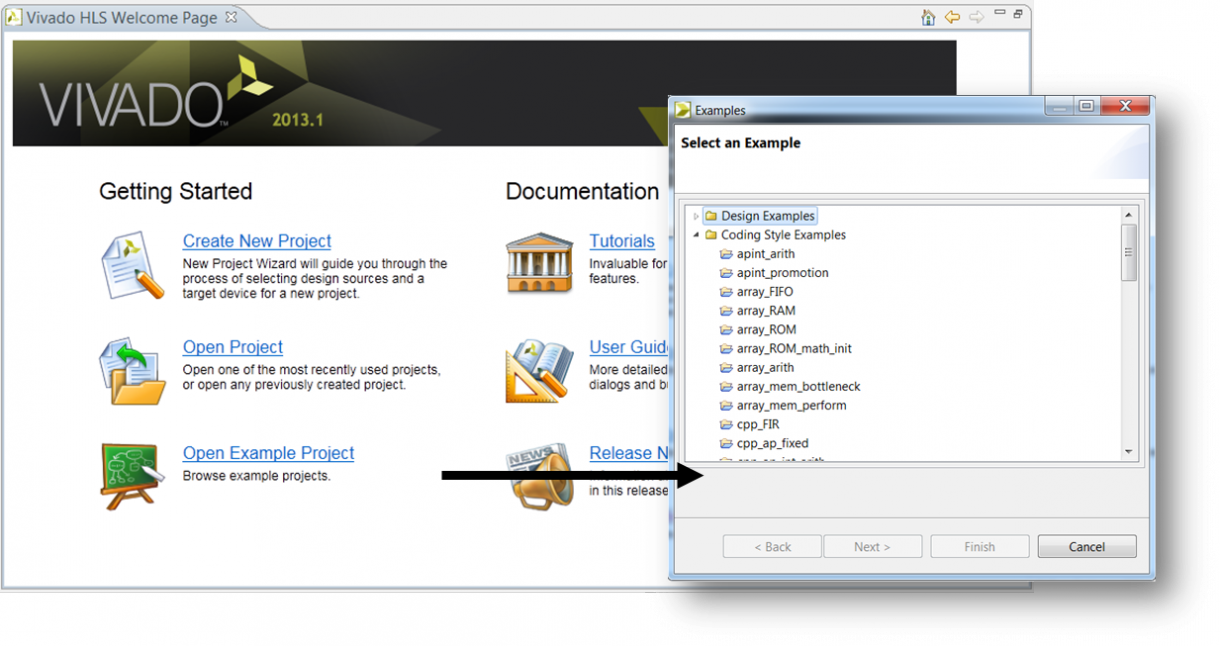

安装Vivado HLS以后, 既包含了20个design example,50个code example:

第二, step by step教程

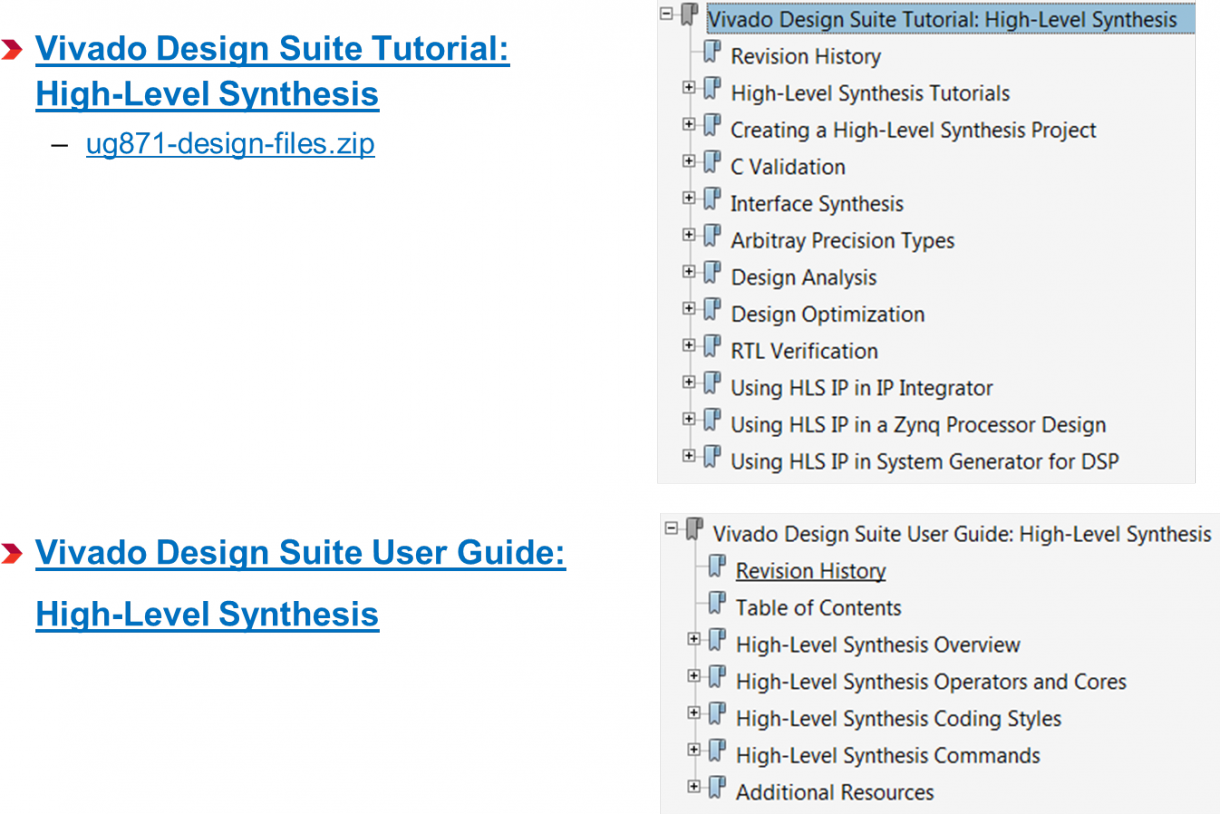

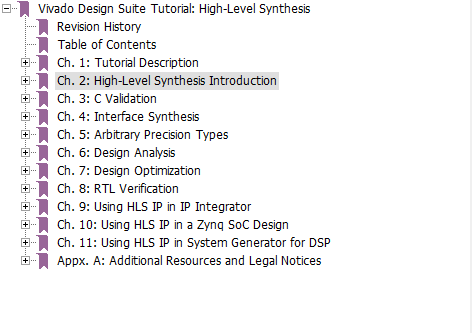

ug871 是xilinx公开提供的HLS教程, 包括11个例子:

C Validation

Interface Synthesis

Arbitrary Precision Types

Design Analysis

Design Optimization

RTL Verification

Using HLS IP in IP Integrator

Using HLS IP in a Zynq Processor Design

Using HLS IP in System Generator for DSP

ug871 : http://www.xilinx.com/support/documentation/sw_manuals/xilinx2013_1/ug87…

参考设计源代码: http://www.xilinx.com/cgi-bin/docs/rdoc?v=2013.2;t=vivado+tutorials

第三, 13个Xilinx专家讲解视频, 包括讲座和演示

地址: www.xilinx.com/training/vivado

1.Getting Started with Vivado High-Level Synthesis

2.Verifying your Vivado HLS Design

3.Packaging Vivado HLS IP for use from Vivado IP Catalog

4.Generating Vivado HLS block for use in System Generator for DSP

5.Generating Vivado HLS pcore for use in Xilinx Platform Studio

6.Analyzing your Vivado HLS design

7.Specifying AXI4 interfaces for your Vivado HLS design

8.Using Vivado HLS C/C++/SystemC block in System Generator

9.Using Vivado HLS C/C++/SystemC based pcores in XPS

10.Floating-Point Design with Vivado HLS

11.Using Vivado HLS SW libraries in your C, C++, SystemC code

12.Using the Vivado HLS Tcl interface

13.Leveraging OpenCV and High Level Synthesis with Vivado

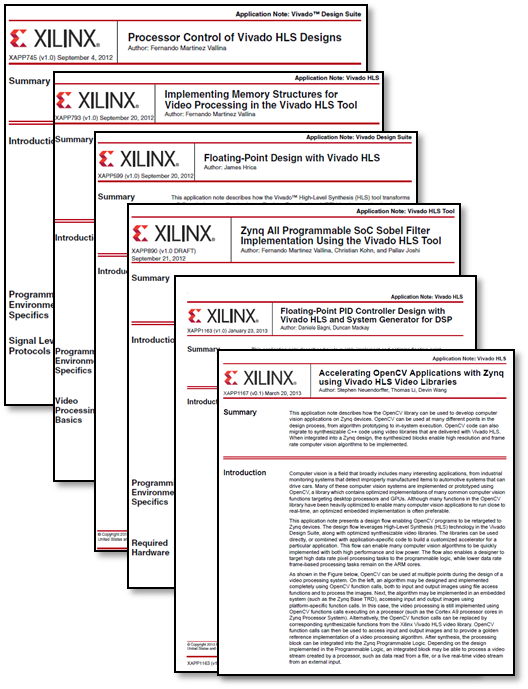

第四, 不停更新的武林秘籍

XAPP745 Processor Control of Vivado HLS Designs

XAPP793 Implementing Memory Structures for Video Processing in the Vivado HLS Tool

XAPP599 Floating Point Design with Vivado HLS

XAPP890 Zynq All Programmable SoC Sobel Filter Implementation Using the Vivado HLS Tool

XAPP1163 - Floating-Point PID Controller Design with Vivado HLS and System Generator for DSP、

XAPP1167 Accelerating OpenCV Applications with Zynq using Vivado HLS Video Libraries

第一个Vivado HLS工程

http://xilinx.eetrend.com/d6-xilinx/webinar/2016-07/10340.html

http://xilinx.eetrend.com/d6-xilinx/blog/2016-12/10734.html

对于Vivado Hls来说,输入包括Tesbench,C/C++源代码和Directives,相应的输出为IP Catalog,DSP和SysGen,特别的,一个工程只能有一个顶层函数用于综和,这个顶层函数下面的子函数也是可以被综合的,会生成相应的VHDL和Verilog代码,所以,C综合后的RTL代码结构通常是跟原始C描述的结构是一致的,除非是子函数功能很简单,所需要的逻辑量很小。 通常在main函数以下的函数都可以被综合,也就是说,并不是所有的C/C++都可以被综合,动态内存分配和涉及到操作系统层面的操作不可以被综合。

本部分结构框架:

Creat New Project新建文档

C simulation

C systhesis

RTL级仿真

IP封装

总结

1.Creat New Project新建文档

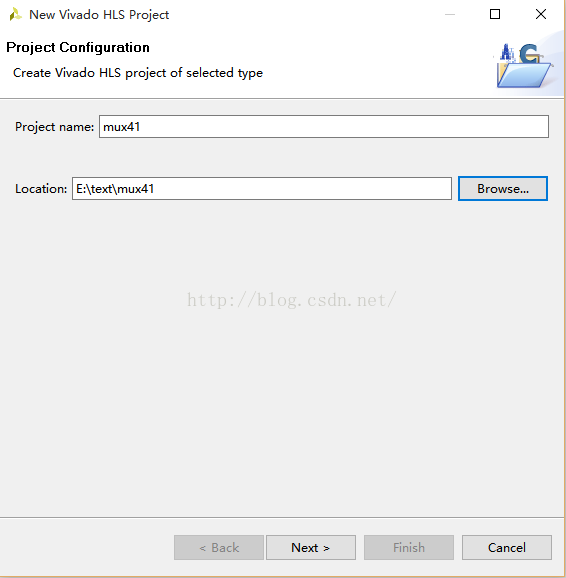

新建一个Project name,点next(这里选取简单的4选1数据选择器为例,主要是说明流程)

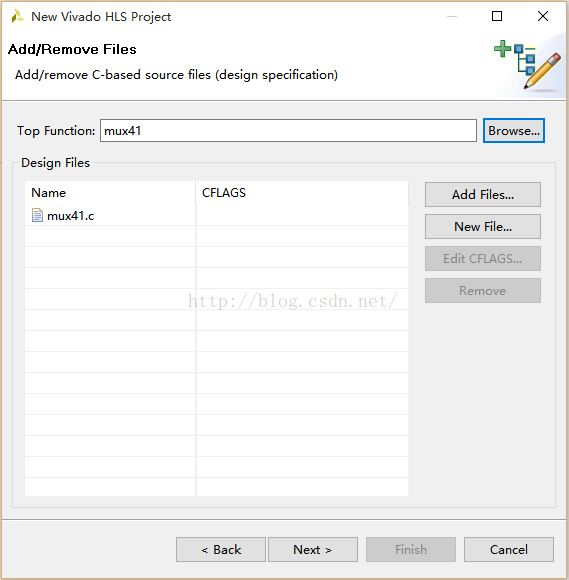

在Add Files里添加mux41.c文件,点next

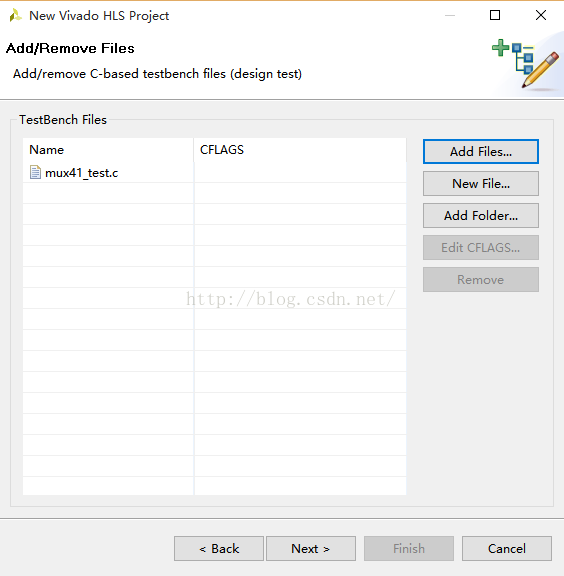

添加mux41_test测试文件,点next

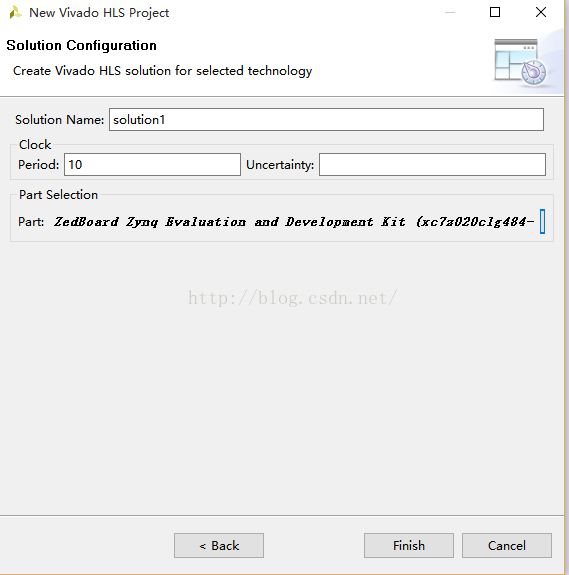

点Part,这里选择Board下面的Zedboard Zynq开发板,然后点OK和finish

注释:

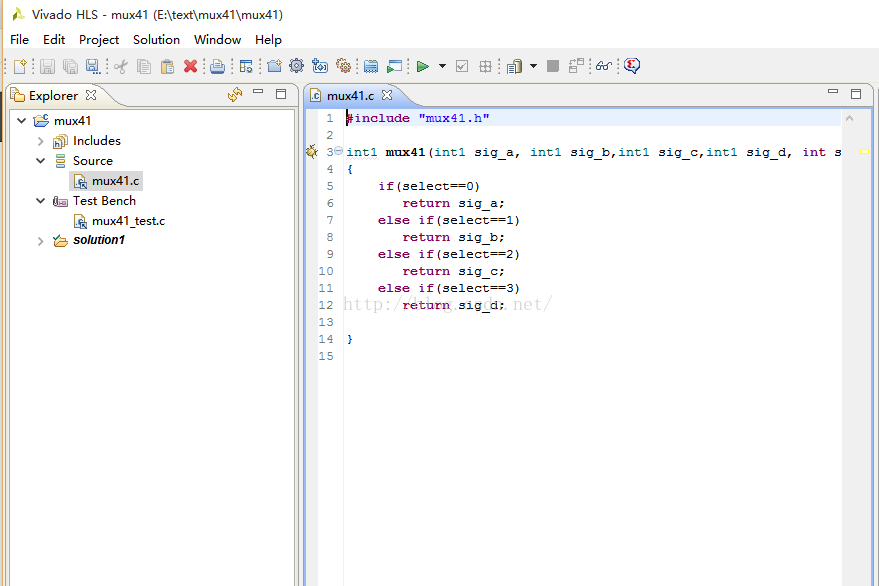

mux41.c代码:

|

|

mux41.h代码:(头文件)

|

mux41_tb代码:(testbench)

|

|

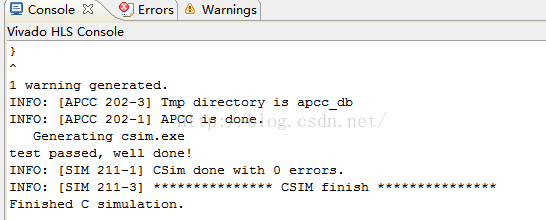

2.C simulation

在菜单里Project>Run C simulation,C simulation可以得到csim文件

从图中看到,可以看到test passed,well done!,证明结果是正确的:

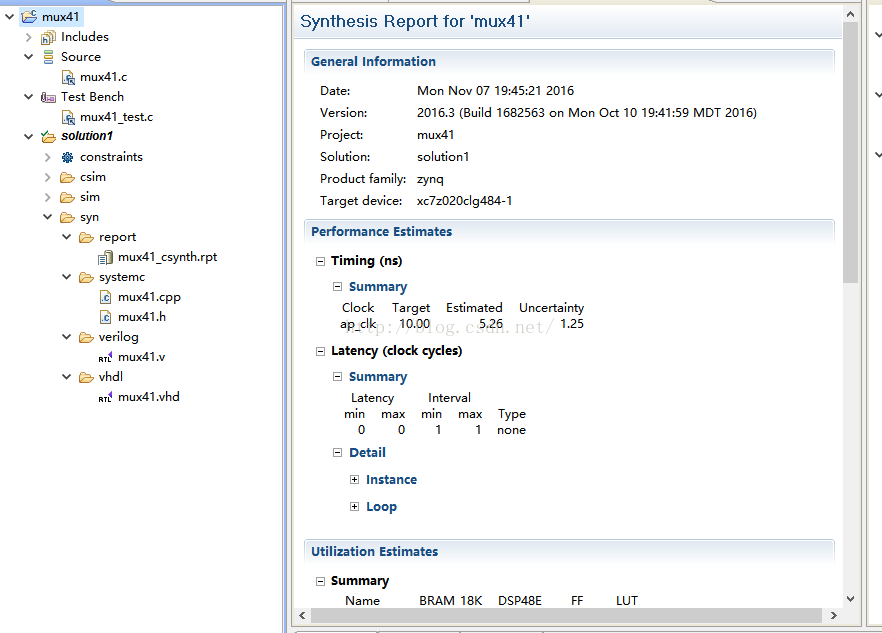

3.C systhesis:

注意综合得到的verilog代码的可读性很差,不需要读懂,所以大多数优化都在C这个层面去做的,下面是综合后的verilog代码:

|

|

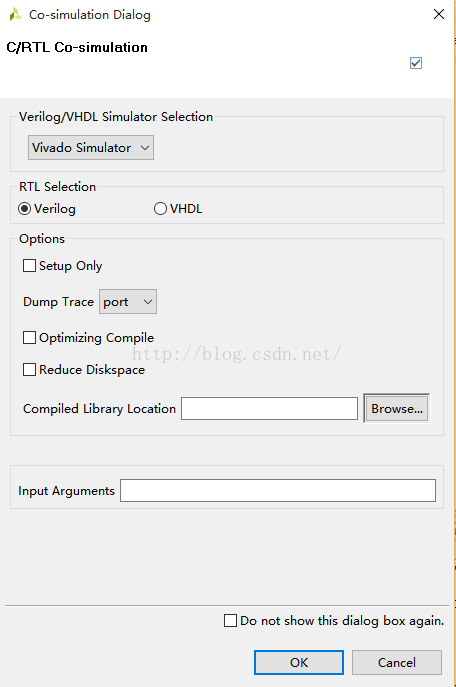

4.RTL级仿真

在菜单里Solution>RunC/RTL cosimulation,需要对Co-similation Dialog设置如下:

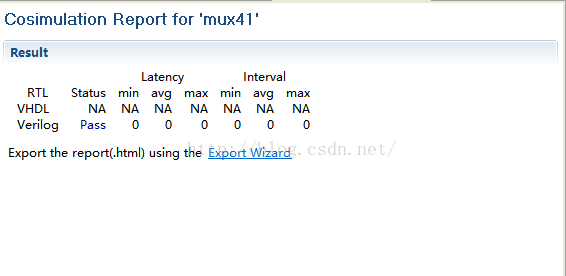

得到如下结果,我们会发现Verilog的Status是pass,证明C/RTL cosimulation成功:

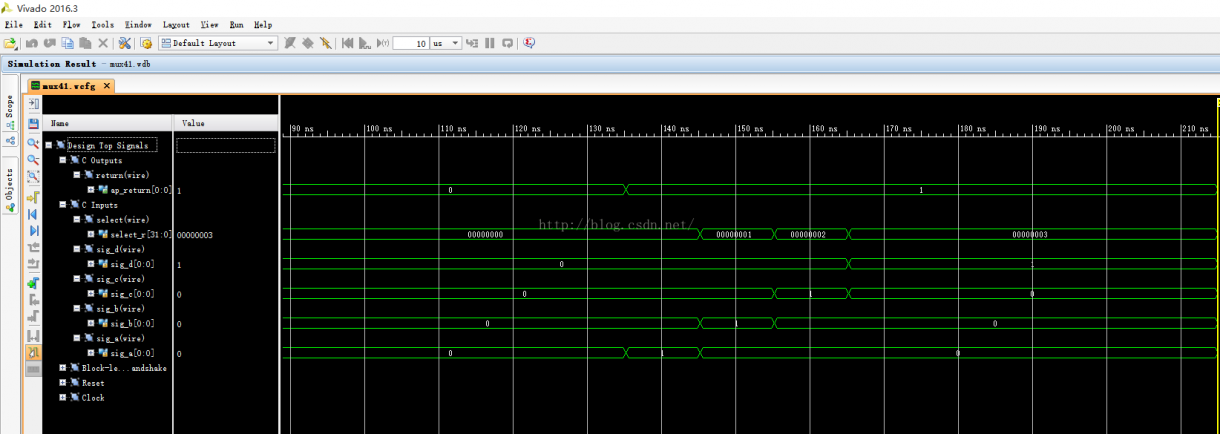

然后我们点开波形查看窗口,此时会自动打开Vivado软件,从图中看到,mux41的功能正确:

5.IP封装

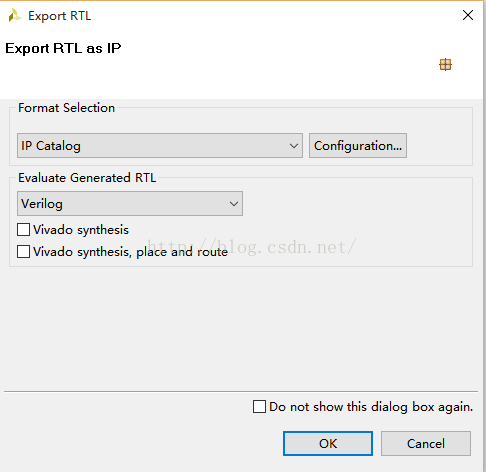

在菜单里Solution>Export TL,设置如下:

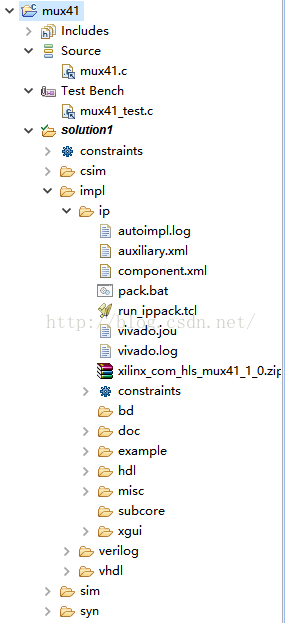

IP封装后,会得到impl文件,其中就有我们所需要的三个子文件ip,verilog,vhdl

总结

事实上,在整个流程中,用户先创建一个设计 C、C++ 或 SystemC 源代码,以及一个C的测试平台。随后需要用 GCC/G++或 Visual C++ 仿真器验证设计的系统行为。一旦行为设计运行良好,对应的测试台的问题全部解决,就可以通过 Vivado HLS Synthesis 运行设计,生成 RTL 设计,代码可以是 Verilog,也可以是 VHDL。有了 RTL 后,随即可以执行设计的 Verilog 或 VHDL 仿真,或使用工具的C封装器技术创建 SystemC 版本。然后可以进行System C架构级仿真,进一步根据之前创建的 C 测试平台,验证设计的架构行为和功能。设计固化后,就可以通过 Vivado 设计套件的物理实现流程来运行设计,将设计编程到器件上,在硬件中运行和/或使用 IP 封装器将设计转为可重用的 IP。随后使用 IP 集成器将 IP 集成到设计中,或在系统生成器 (System Generator) 中运行 IP。

HLS进阶学习

初步学习计划

HLS说到底是一个工具,作为工具,应用为先。

第一步 利用教程和例程跑一个hls仿真

详情参考ug871第二章 create a high-level synthesis project

以下仅对值得注意的地方进行记录

很好,我点进上文的参考代码链接,给我出现了以下界面

我觉得事情不简单,下拉以后

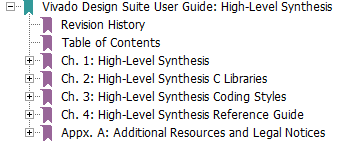

好的吧,出现最新版教程了。左边侧栏勾选tutorials,然后把document type 那边的user guides去掉。往下拉你就可以看到清纯不做作的ug871 2018.2。

………………换文档肯定要跑路的啊!(不是)换文档肯定要看看有什么区别的啊!

2018.2

2013.1

初步判断没什么实质性区别,那好,我去看看操作。其实本来差别就不可能很大,主要是怕有一些操作不同。这个时候第一步就是打开我的垃圾 vivado hls 2016.1,暗中观察一下初始GUI页面跟哪一版的教程更像。

然后我觉得我应该用新版教程了(っ•̀ω•́)っ✎⁾⁾。接下来这句话:详情参考ug871 2018.2 ch.2 hls introduction

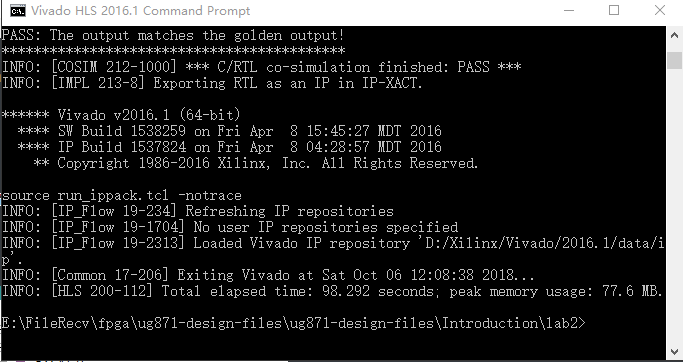

哦好的吧,我本来想搞一个能看Waveforms的工程出来,然后发现ch2这章introduction的三个lab是在教软件使用方法。好吧,那我放一个我lab 2成功的截图好了。

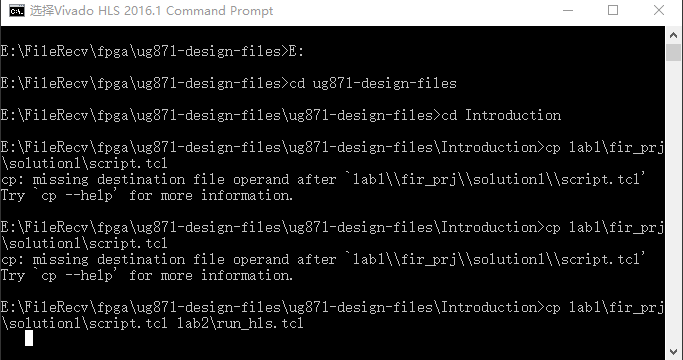

说一下体验,教程还是很详细的,基本都很顺。除了lab 2用commad prompt的时候,出了一点小问题。因为第一步要定位到introduction文件夹里,我一开始用cd 命令……然后就一点都不ok,查了才发现windows cd命令只能切当前盘内路径。

然后如果像我一样不按原设定路径安装的话,这部分修改大致如下:

因为我混乱的路径就是……

E:\FileRecv\fpga\ug871-design-files\ug871-design-files\Introduction

这样的啊,然后我又习惯性地把fir_prj放到我平常放代码的地方,就不在lab1目录下。为了完成这个实验,那当然是!复制过来!!!

之后操作就一切正常。

总之官方教程文档很详细。只是编一个初始的小工程编译就花了不少时间,我已经感受到了来自vivado的威胁(T▽T)

心怀电路写C第一步,完成。

第二步 利用手上的ug871和ug902文档研究官方例程和语法约束

ug871官方例程教程

ug902语法约束

第三步 将hls运用在参赛项目上

过程记录如下